#### **CMOS MAPS Silicon Pixel VTX for SuperB**

Gary S. Varner Open Collaboration Meeting #2 July 4<sup>th</sup>, 2008

- Issues

- CAP series

- Evolution of strategy

- Desire for improvement

- Hexagonal Pixel (hixel) [CAP7]

- Next generation

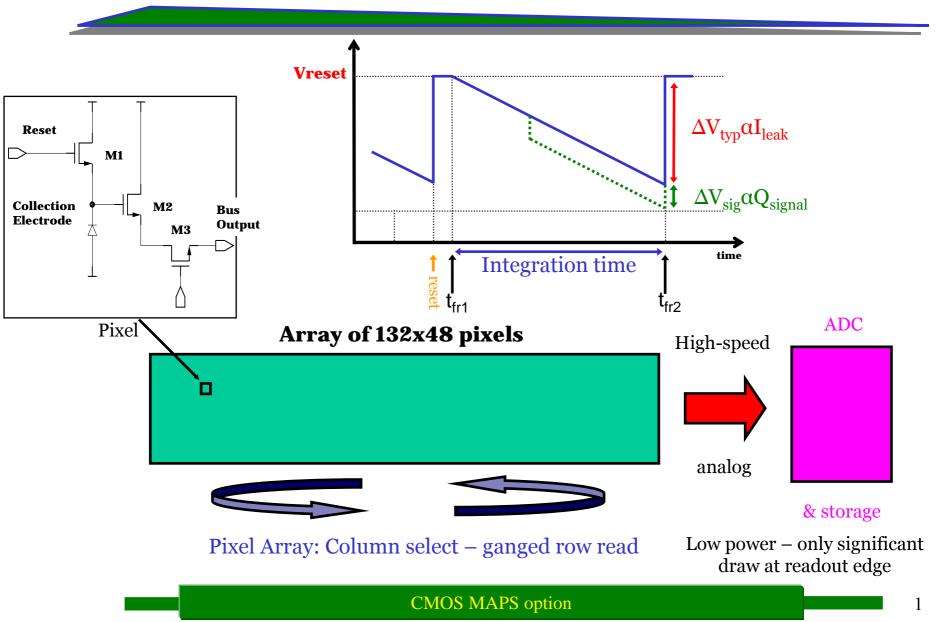

# Continuous Acquisition Pixel (CAP)

# sBelle CMOS Pixel Study Activities

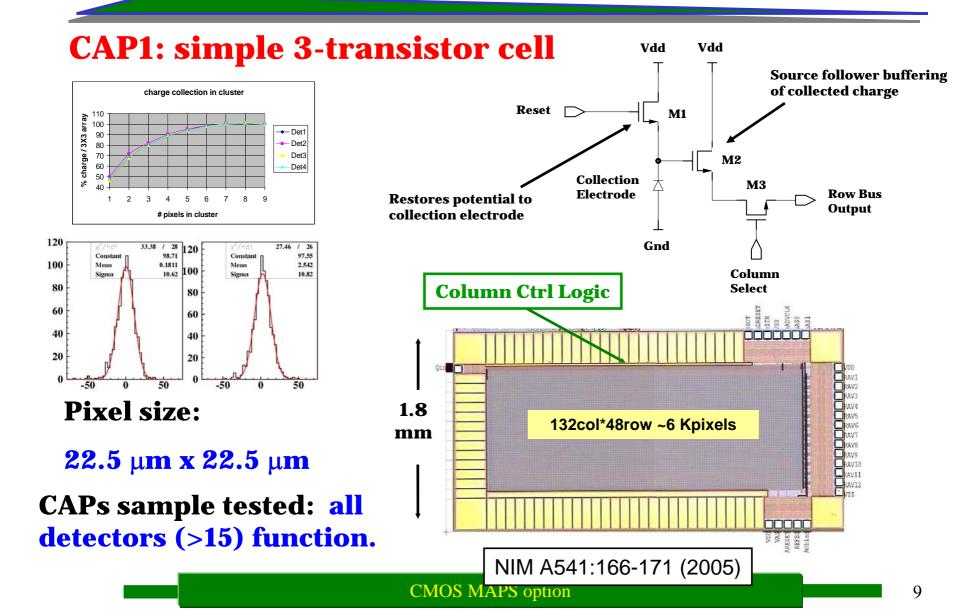

- CAP1/2 [MAPS technology] Studies

- Characterization of CAP1 in test beam [NIM A541 (2005) 166]

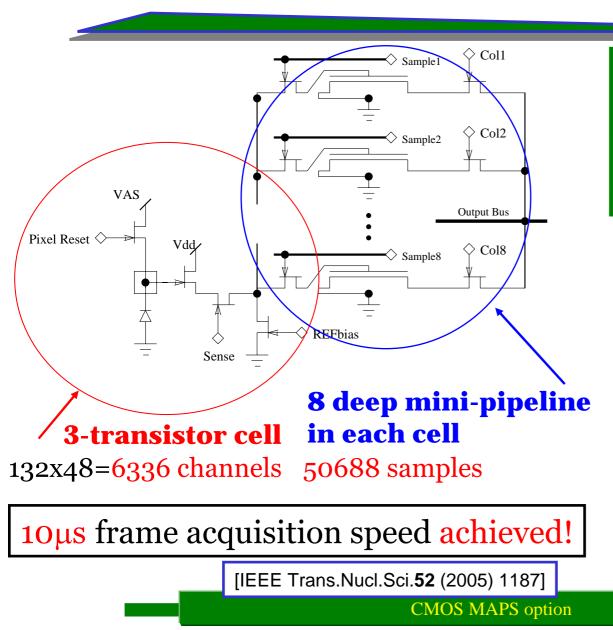

- Study of radiation hardness/storage [IEEE Trans.Nucl.Sci.52 (2005) 1187]

- Storage density/max. pipeline depth studies

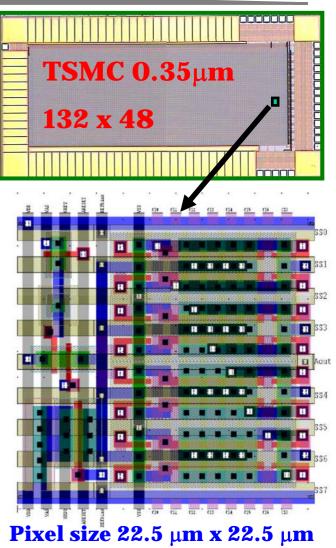

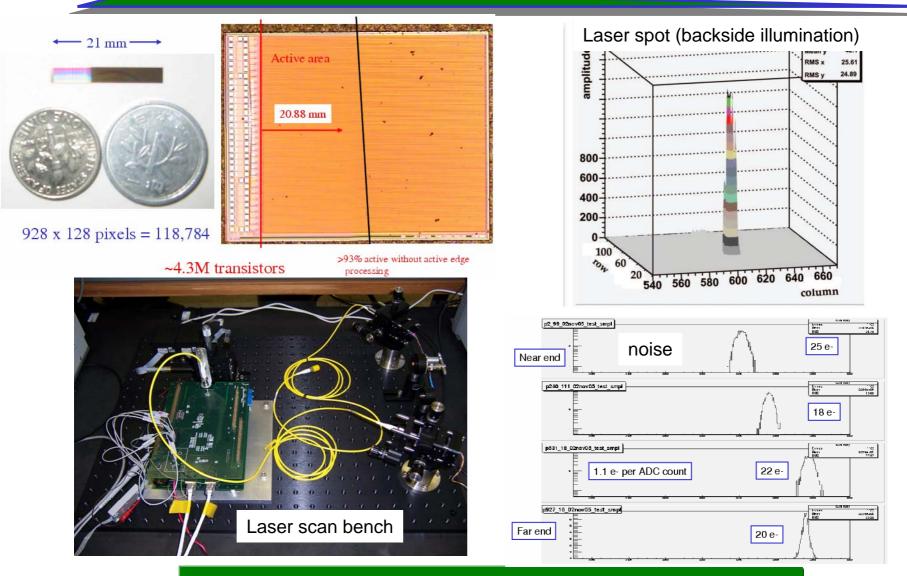

- CAP3 "full size" Detector [NIM **A565** (2006) 126]

- Development of laser scan system for systematic studies

- Systematic scan and study of transfer rate and signal uniformity

- Non-uniformity and transfer limitations observed

- CAP4 AMS 0.35um Opto [NIM A568 (2006) 181]

- Study of new analog storage/readout evaluation started

- CAP5, 7 SOI prototypes studies continue

- Study of 0.15um OKI process [SLAC-PUB-12079]

- Fully depleted, time-space correlation storage study

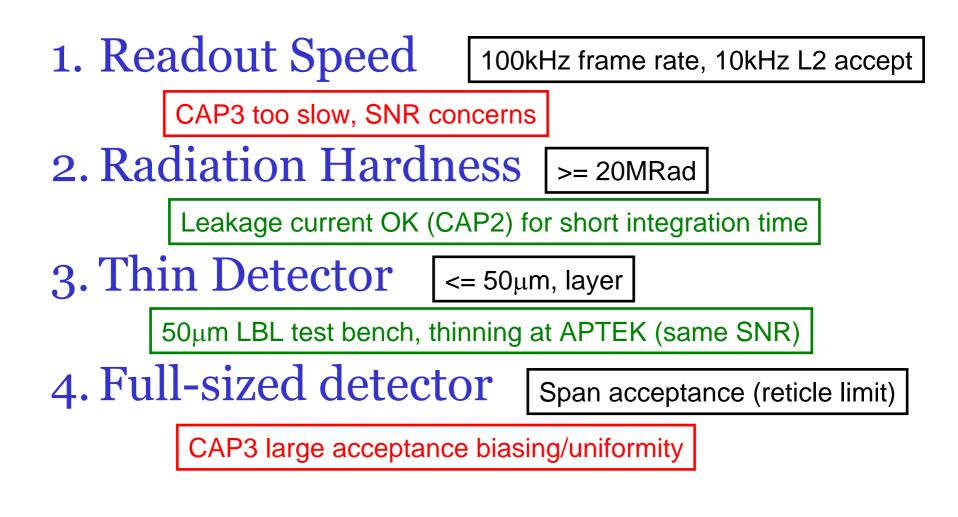

### Critical R&D Scorecard

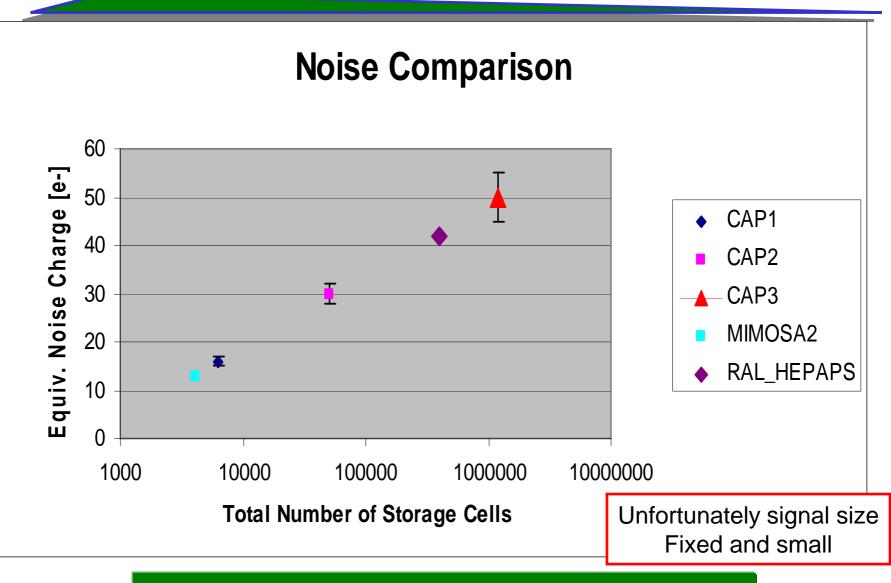

#### Noise (ENC): Summary of MAPS

**CMOS MAPS option**

#### sBN0007 for details

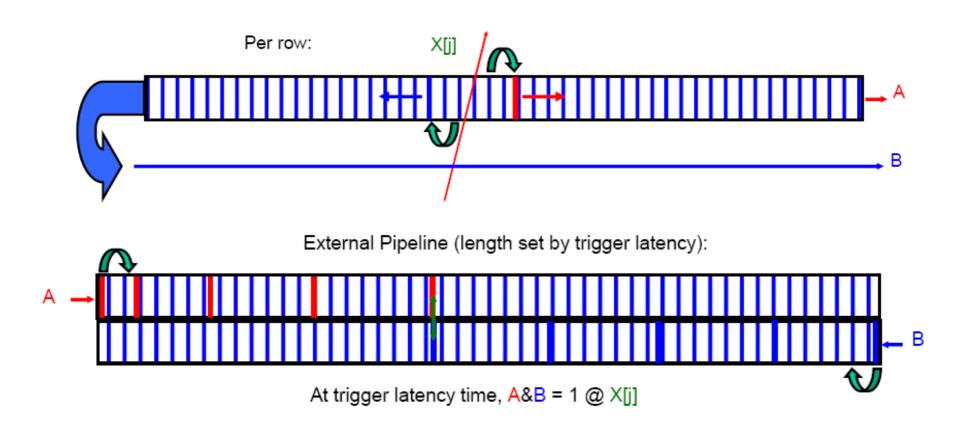

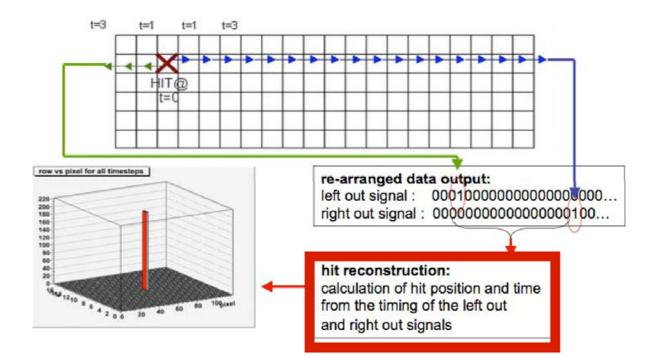

hit reconstruction for a binary detector with time encoding

you are familiar with this:

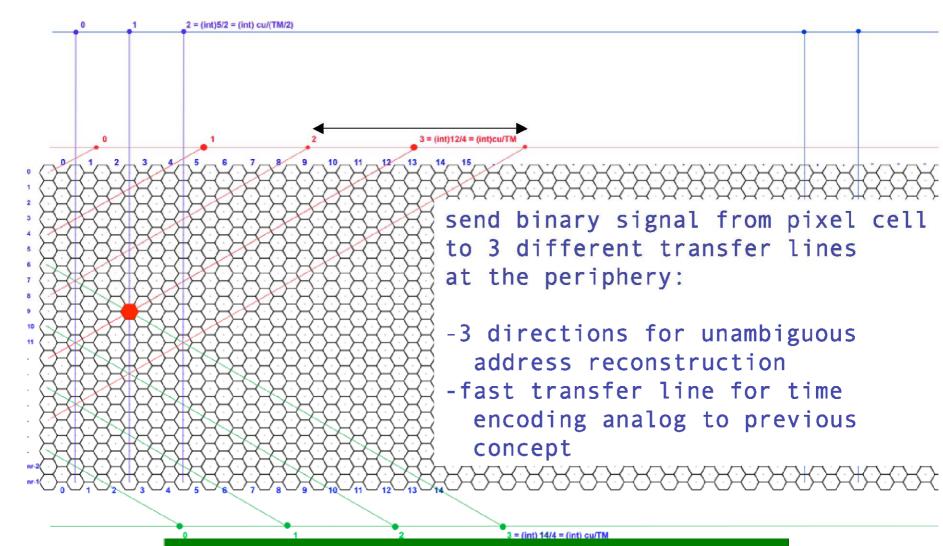

# hexagonal pixel layout with external transfer lines

**CMOS MAPS** option

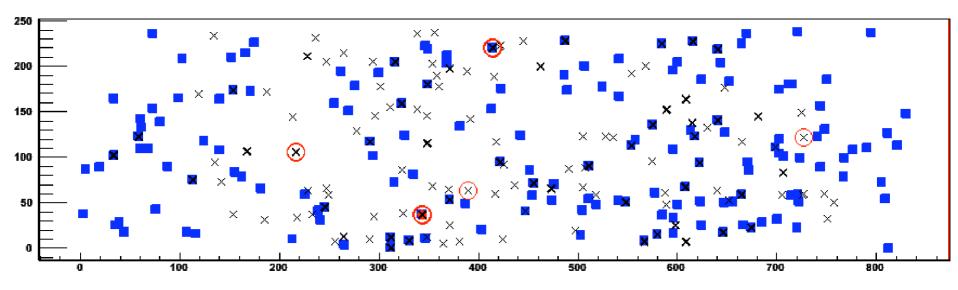

#### example event (TM = 12)

- background

- seeded hit

- $\boldsymbol{X}$  all reconstructed hits in time window

$\bigcirc$  reconstructed @ t<sub>trig</sub>

7/2/08 page 17

# **CMOS** Option Summary

- Need to demonstrate binary can work

- SNR is still an issue

- SOI variant probably more realistic

- Next OKI submission

- TSMC 0.35um opto submission end of July

- Issues of cross-talk, threshold dispersion

- Binary has possible benefit

- Reduced data size

- Intrinsic Resolution degradation not critical

- Original benefit of commercial CMOS MAPS

# Cont. Acq. Pixels (CAP) 1 Prototype

#### CAP2 – Pipelined operation

#### CAP3: Full-size Detector Test/Lessons learned

**CMOS MAPS option**

# **Pixel Occupancy Scaling**

- Work from following assumptions:

- Super-B canonical x20 background increase

- Assume 10% Layer 1 occupancy as "current"

- Strip area (L1) =  $85mm \times 50\mu m = 4.25M \mu m^2$

- Pixel spatial reduction:

- Pixel area =  $22.5\mu m \times 22.5\mu m = 506 \ \mu m^2$

- Reduction factor ~8400

- Low E  $\gamma$ , reduced cross-section (~3% active thickness)

- Pixel temporal loss:

- 0.8µs SVD vs. 10µs PXD (could be improved)

- Increase factor ~ 12.5

- Grand total:

- 10% \* 20 \* 8400<sup>-1</sup> \* 12.5

- Can expect ~ 0.3% occupancy (no ghosting)

### CAP5

#### **BINARY READ OUT**