# Common readout and timing distribution

Mikihiko Nakao (KEK IPNS) July 4, 2008 2nd Open Meeting for proto SuperBelle Collaboration mikihiko.nakao@kek.jp

### **Baseline design**

- Capable at 30 kHz trigger rate (nominal maximum)

- Event-by-event trigger-busy handshake,  $\sim 1\mu$ s deadtime is okay, but the current busy collection scheme already requires  $\sim 1\mu$ s

- No extra time to hold busy by the readout system, so the readout system should have a large enough buffer in order to avoid a long busy time

- Pipelined digitization, timing w.r.t. the system clock

- Most detectors do not care a clock jitter of O(100ps)

- TOP detector requires O(10ps) time resolution

# **Timing to COPPER**

Q-to-T + FASTBUS TDC was an excellent technology in 1995

- Problems: deadtime, old and decaying, and availability

- Solution: COPPER?

*Q-to-T modules were different for each detector, so could be the FINESSE module?*

It turns out that many of the detector people are willing to digitize data near the detector — this makes COPPER just a digital-to-network converter.

- New questions

- Could the digital transfer link (and FINESSE) be common?

- How to deliver timing signals to near-detector sites

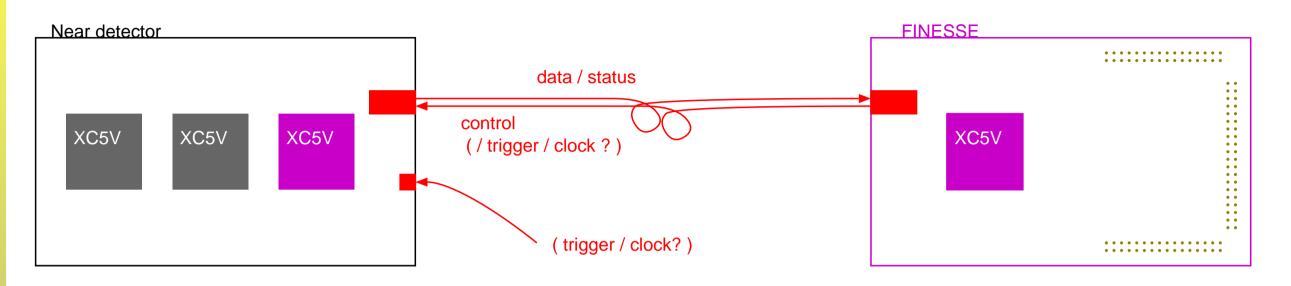

## **Remote FINESSE**

- Extend the FINESSE function over an optical link + timing line

- Need a very simple interface similar to FINESSE/COPPER interface at the remote card

- Colored part could be standardized

- O(25ch) (or O(50ch)) per such a card?

- 600 (or 300) links for a 15k ch CDC (150 or 75 COPPERs)

### **Technology choice**

- Xilinx RocketlO at both ends

- RocketIO GTP (up to 3.75 Gbps) or GTX (up to 6.5 Gbps)?

GTP is good enough (FINESSE doesn't have such a bandwidth)

- Optical tranceivers 2.5 Gbps SFP tranceivers?

- 2.5 Gbps  $\Rightarrow$  ¥30,000.-

- 4 Gbps  $\Rightarrow$  ¥50,000.-

- 10 Gbps  $\Rightarrow$  >¥200,000.-

- FPGA choice Virtex5 LX30T? (¥35,000 / chip)

- already >¥100,000 /link, faster options are unrealistic

## Protocol

#### Minimum requirements

- Simple protocol to encapsulate a variable-length data

- Link establishing scheme

- Error detection

- Recovery from error without stopping data taking

- Predictable latency

- Command / status embedding between the data packets

- Desirable

- Clock recovery

- Not needed

- Error correction and retransmission

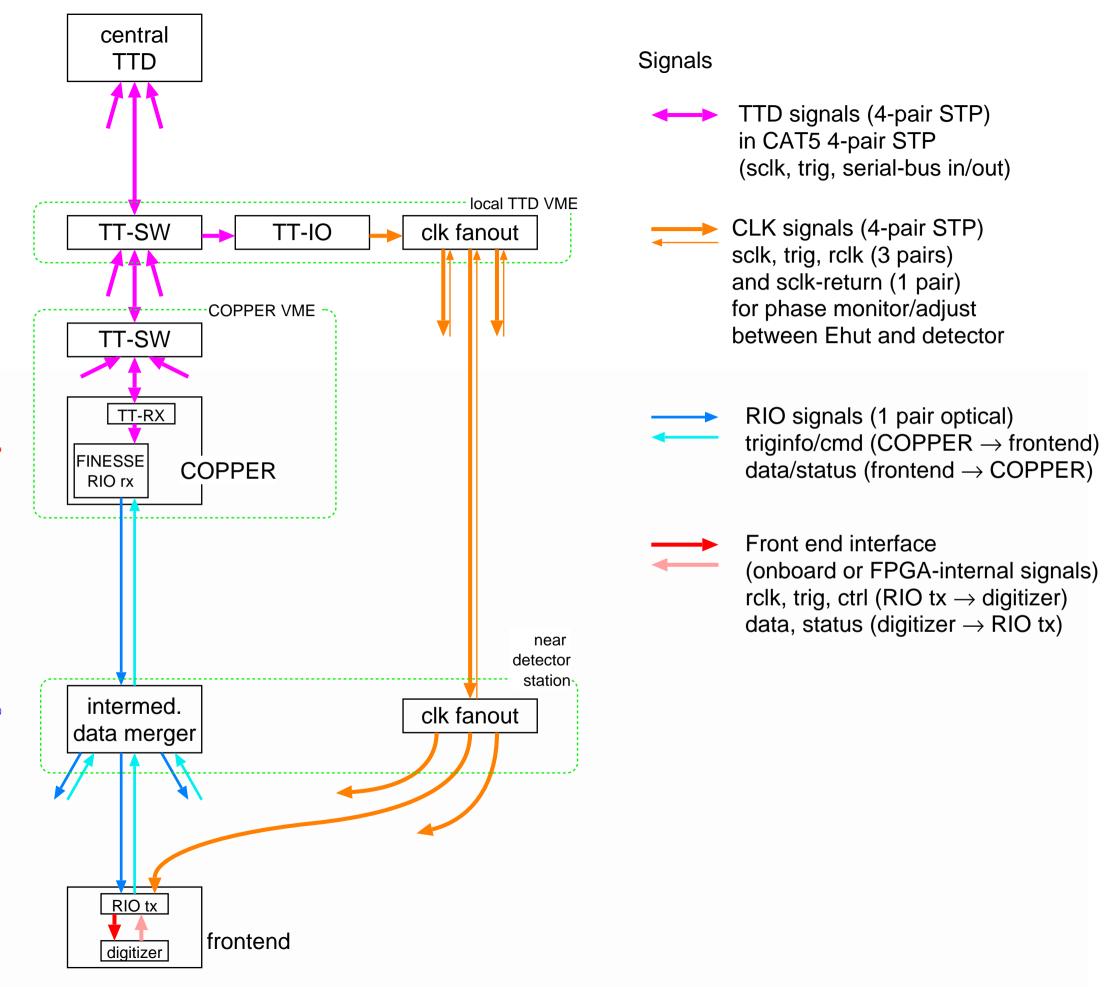

## **Timing distribution to detector**

- An extra set of signals to the detector

trigger, clock, clock-return, reduced-clock

(4 pairs of COPPER cables, i.e., standard STP cable is suitable)

- Need only one cable from Ehut to a site

A new timing distribution module has to be developed

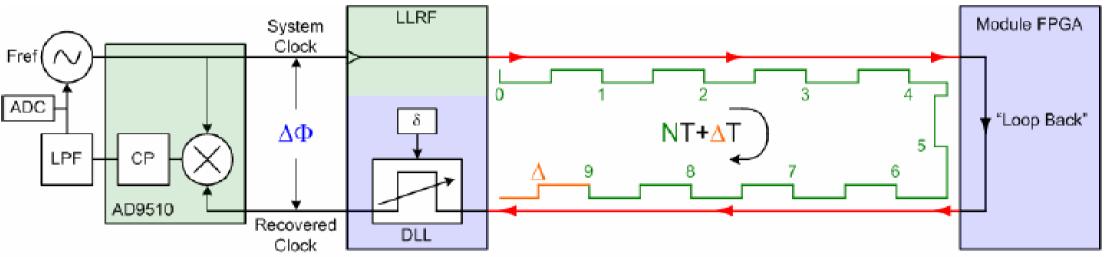

- Clock issues

- Correction for the clock phase drift (clock-return  $\Rightarrow$  PLL)

- Can't we just receive the KEKB clock at the detector?

- No good measurement tool in hand

- Trigger issues

- Trigger timing is better distributed through a dedicated line, unless SERDES latency is tolerable

- Need another path to send the trigger id

http://indico.cern.ch/conferenceDisplay.py?confId=28233

**Requirements at Receiver:**

- FPGA with high speed serial I/O

- External PLL with good VCO

**Requirements at Master:**

FPGA with multiple high speed serial I/O's

What you get:

- Frequency Recovery (at noise quality of VCO)

- Line length drift compensation

- Multiple FPGA clocks aligned to 1/256 of a cycle (16 ps @ 240 MHz)

- Time accurate to 1/256 of a cycle (for stamping and event scheduling)

- It is possible to recover a 240MHz clock from a 2.4Gbps rocketIO (no need of external link?)

- Maybe we can consider running RocketIO at KEKB RFx4 (2.032 Gbps)

### Intermediate merger?

- We may want an event building at the RocketlO level, to reduce number of fibres from the detector to COPPER

- A-RICH would need such a system

- No detail has been discussed

### Plans

#### RocketIO tests

- A Virtex2Pro test board is in hand (with a test firmware)

- TT-IO module has a SFP port for RocketIO so far, not successfully tested ⇒ a good example to further understand RocketIO

- Buy a Virtex5 test board if needed

- Built a Virtex5 test board

- Need to collect detector requirements

- Number of channels, typical data size, latency

- Digitization clock

- Required time jitter

- Need to decide the buffer size for deadtime free data link