### **Results of the run with the new electronics**

A.Kuzmin, Yu.Usov, V.Shebalin, B.Shwartz

- 1. New electronics configuration

- 2. New electronics in the experiment

- 3. Results on the consistency, timing and noise reduction.

- 4. Operation without injection veto.

### **New+ ECL electronics**

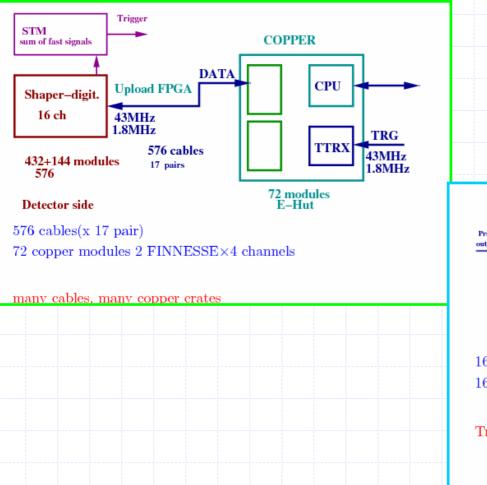

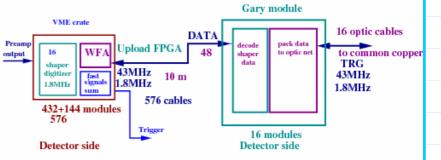

#### New electronics

#### Very New electronics

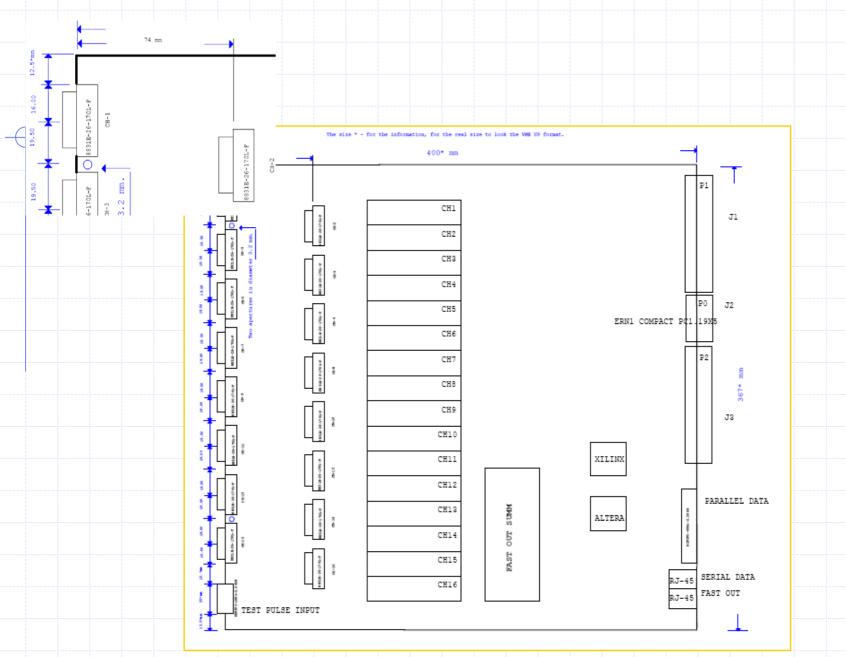

16 cables(optical)

16 Gary modules  $\times$  (48) channels

Trigger, uploading, protocol..? under design

# **Readout scheme**

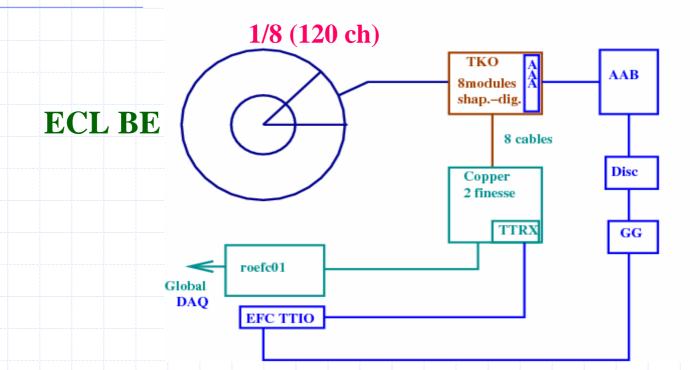

(was tested with cosmic ray runs during summer shutdown)

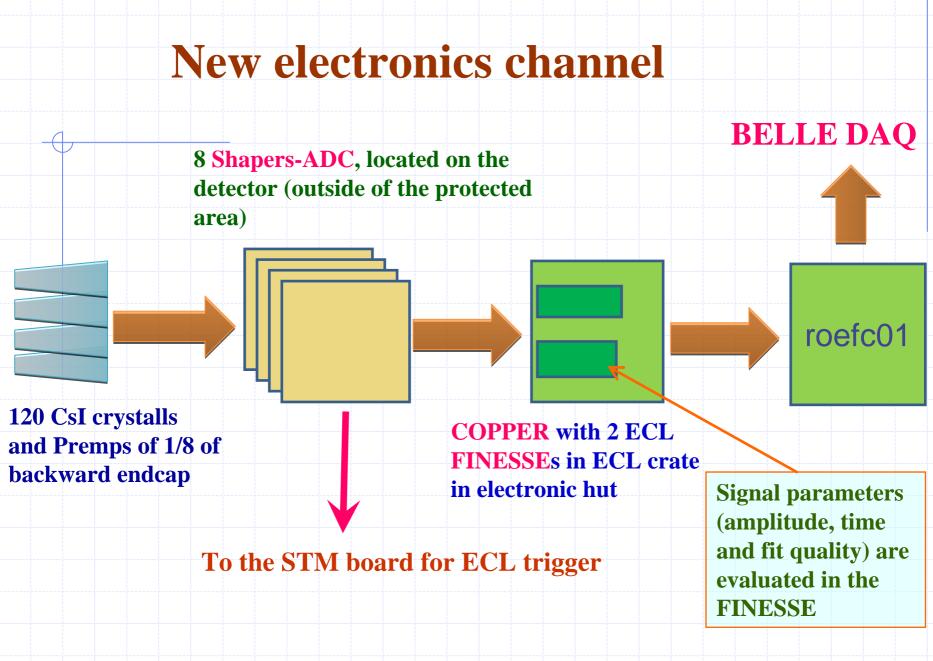

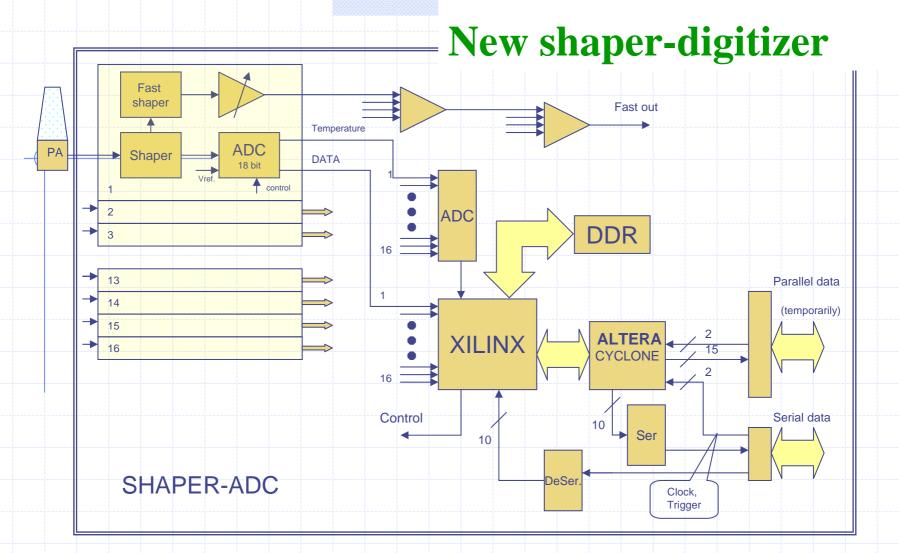

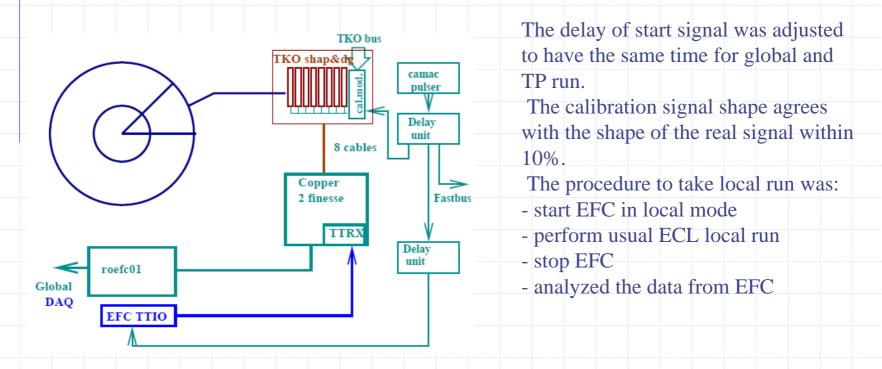

8 Shaper digitizer were connected to ECL B3 sector (120 channels) Copper module installed in the crate near FB rack The Copper is readout by EFC PC roefc01 Trigger: Normal cosmic trigger for global run.(or of all trigger cells)

Dec.11, 2008

Dec.11, 2008

ECL parallel session, Super B

4

### **Parameters determination**

$\begin{array}{l} Algorithm details\\ \chi^{2}(A, p, t_{0}) = \sum_{i,j} (y_{i} - Af(t_{i} - t_{0}) - p) S_{ij}^{-1} (y_{j} - Af(t_{j} - t_{0}) - p) \rightarrow \min\\ S_{ij} = \overline{(y_{i} - \overline{y})} (y_{j} - \overline{y})\\ f(t) - \text{counter response}\\ Af(t_{i} - t_{1} - \Delta t) = Af(t_{i} - t_{1}) - A\Delta tf'(t_{i} - t_{1}) = Af(t_{i} - t_{1}) + Bf'(t_{i} - t_{1})\\ \text{where } t_{1} - \text{initial time (trigger time)}\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0\\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0 \\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0 \\ \sum_{i,j} f_{i} S_{ij}^{-1} (y_{j} - Af_{j} - Bf'_{j} - p) = 0 \\ \sum_{i,j}$

5

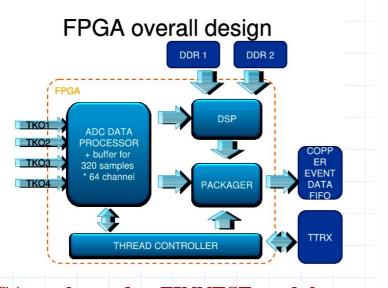

**FPGA** are located at FINNESE module  $\sum_{i,j} S_{ij}^{-1} (y_j - Af_j - Bf'_j - p) = 0$ The algorithm of energy and time reconstruction was implemented.

#### The online software allows:

- To set preliminary sparsification threshold (before FPGA processing);

- To set output sparsification threshold (after FPGA processing), before recording to

COPPER buffer;

To record amplitude, time and quality, reconstructed at FPGA;

- To save raw sample informatin (amplitudes of 16 points) for each or some fraction of events.

- According to simulation the algorithm works upto 50 kHz with occupancy < 1=3.</li>

Dec.11, 2008 ECL parallel session, Super B

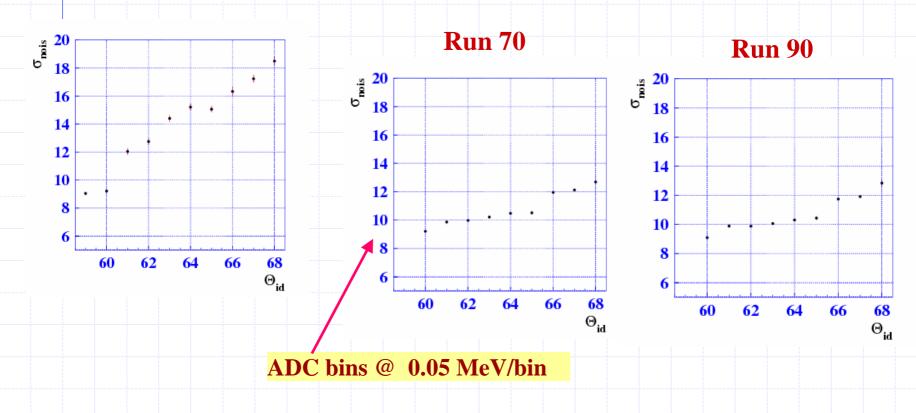

## **Electronics noise**

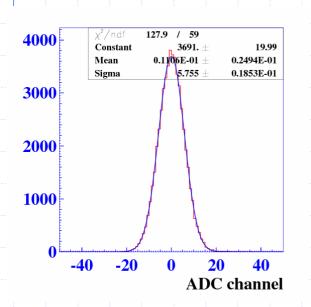

**Incoherent noises :** 5.7 channels(330keV) (outer layers) 7.1 channels(410keV) (inner layers) 10% higher than expected Obtained at the summer tests with cosmic rays

**Coherent noises :** 1.2 channels(70 keV) for 16 channels (1 module) 0.6 channels(30keV) for 120 modules On test bench we got 1.0 channel Calibration module had given big noise and was modied to have possibility to dissconect by relay.

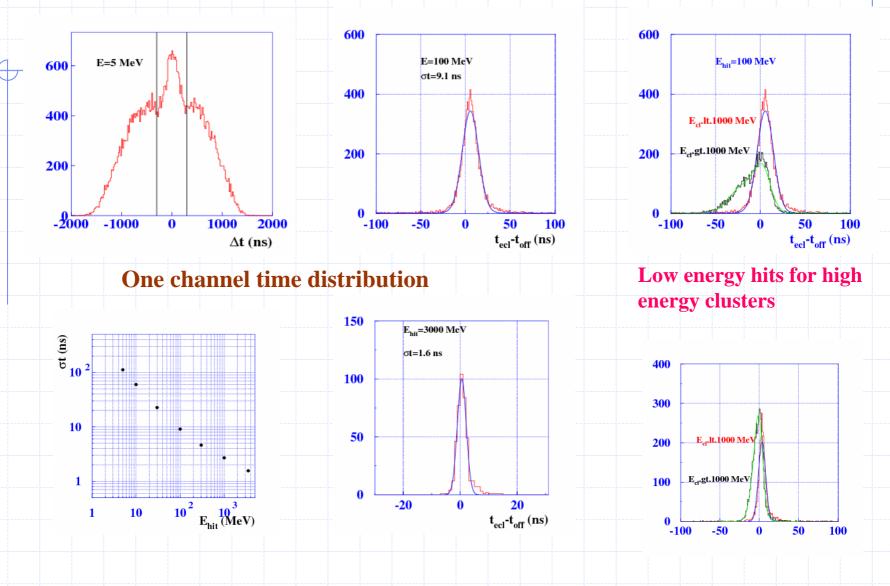

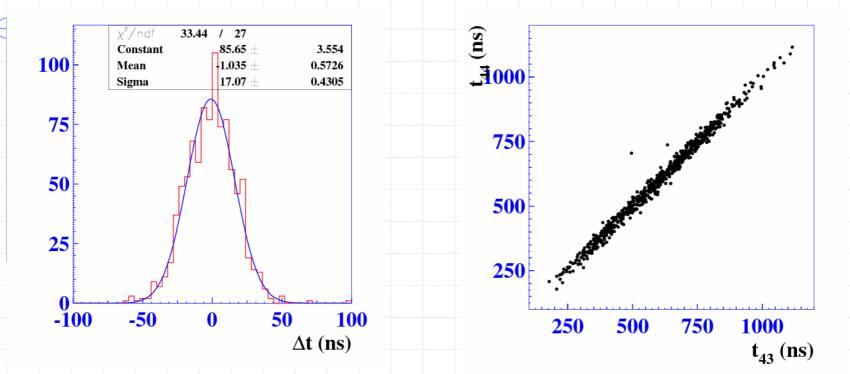

The time resolution per counter is  $17/\sqrt{2}=12$ ns as expected for 35 MeV energy deposition

Dec.11, 2008

## **Test with new ECL electronics**

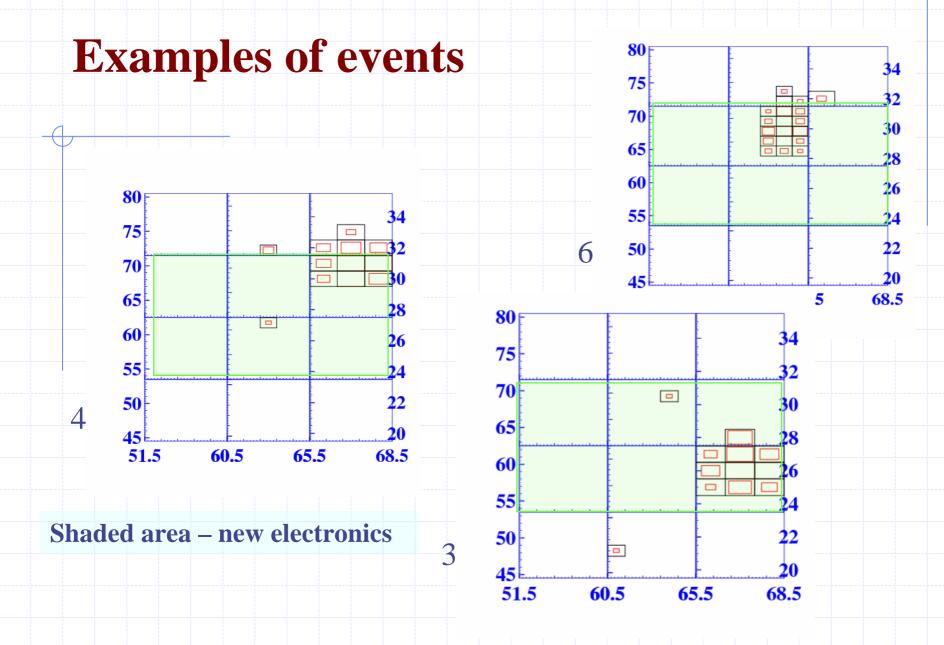

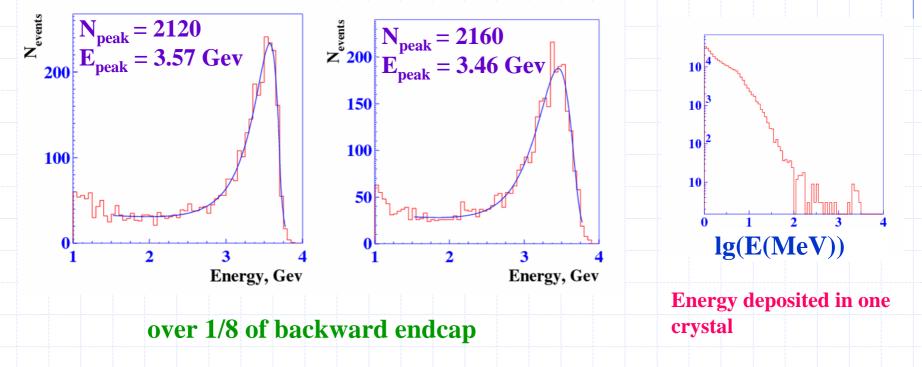

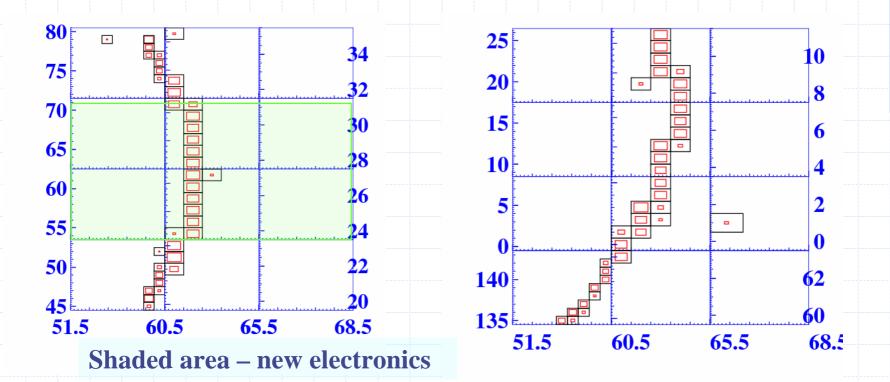

Since beginning of this experiment (exp.67) up to Oct.23, morning, ECL was running with 120 channels (1/8 of the BE) connected to 8 new shaper-digitizer boards, read out by the copper module. Other ECL channels were in the usual status. In this configuration we collected about 965 pb<sup>-1</sup> of the statistics.

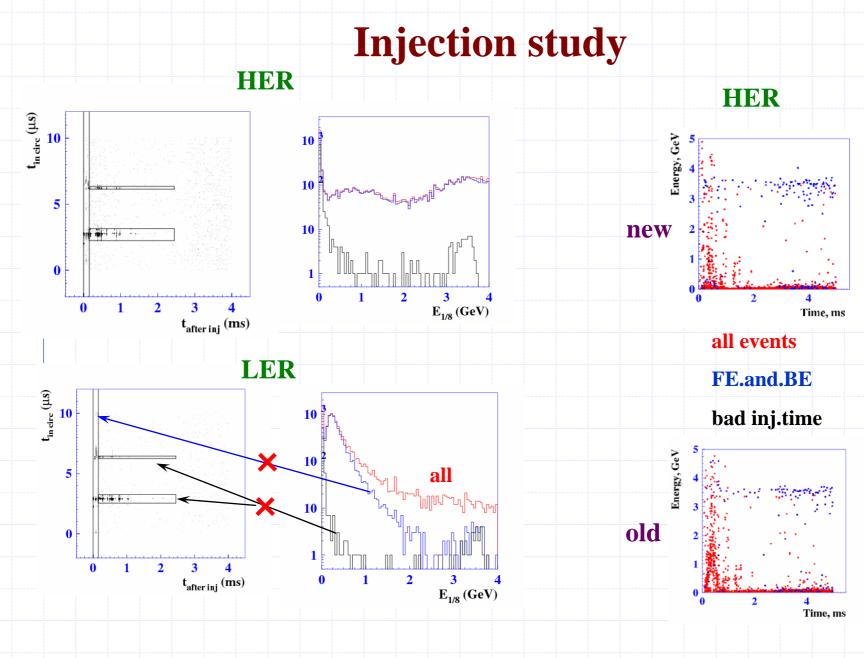

From this data 4 runs with 26 pb<sup>-1</sup> was recorded without injection veto.

On Oct.23, during the maintenance time, we replaced the new electronics with the old one. Nakamura-san analized the data from the local run performed after replacement and confirmed that all changed channels

are alive.

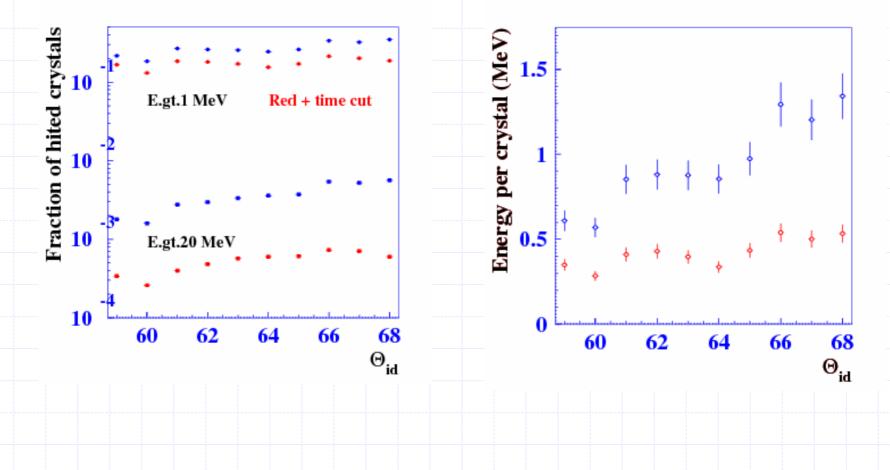

### **Energy deposition**

### old new

### **Timing and background**

Dec.11, 2008

#### **Background reduction**

#### Noise measurement

old electronics

new electronics

Dec.11, 2008

ECL parallel session, Super B

13

#### Summary of the new electronics tests and plans

- System works and allows to record data from COPPER

- The data evaluated by FINNESSE are consistent with that taken by the old electronics

- The recorded data shows parameters close to expected.

- Data quality vs. injection time are studied. A decrease of veto gate looks to be possible.

- **Plans:**

- Further study pile-up noise suppression

- To analyse data with sampling storage to get information about time noise correlation, as well as fit procedure and hardware reliability.

- To analyse run without injection veto.

- Implementation of the data from the new electronics to the standard data processing procedures: cluster reconstruction, Bhabha calibration etc.

Dec.11, 2008

Status: the board design has been completed and agreed (Yu.Usov) with the manufacturer-company. Now the formal contract is needed to start the production of the 2 first version boards.

Dec.11, 2008

# Back up slides

# Local run

For FASTBUS ECL electronics we perform local runs to monitor pedestals ant gain.

For COPPER electronics the pedestals are obtained from the t.

We need the TP calibration to monitor gain.

ECL local run has complicated structure and we use simplied procedure.

### **Summer time - goals of the test**

In the last summer shutdown 120 channels of the ECL BE were connected to the new shaper-digitizer boards. The goals of the test were:

Measurement of the noise and coherent noises at detector

- Test of reliability of the readout at high rates

- Test of calibration procedure

- Long term test of the FPGA logic

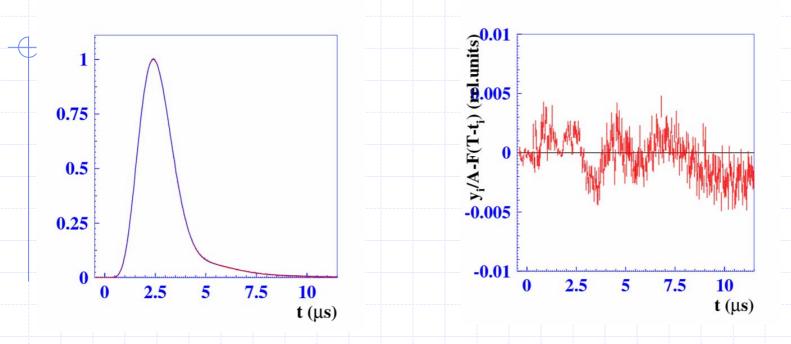

Signal shape

The signal shape was measured with cosmic rays Software was installed at roefc01 Trigger was taken from 1 TKO crate and store several local runs Using stored data we fit time shape of the signals ans prepare DSP les for FINNESSE

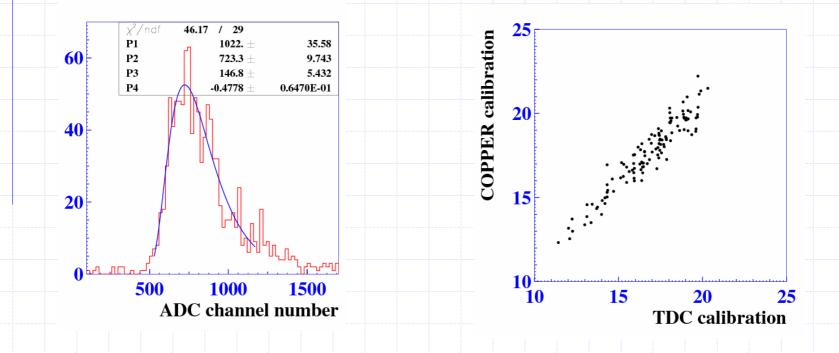

#### **Calibration with cosmic rays**

# Consistency

We searched for possible events with some inconsistence in FASTBUS and COPPER data

## **Electronics noise**

#### Incoherent noises : 5.7 channels(330keV) (outer layers) 7.1 channels(410keV) (inner layers) 10% higher than expected

#### **Coherent noises :**

1.2 channels(70 keV) for 16 channels (1 module)0.6 channels(30keV) for 120 modulesOn test bench we got 1.0 channelCalibration module had given big noise and wasmodied to have possibility to dissconect by relay.

## Timing

The time resolution per counter is  $17/\sqrt{2}=12$ ns as expected for 35 MeV energy deposition

Dec.11, 2008

ECL parallel session, Super B

23

Dec.11, 2008

#### ECL parallel session, Super B

24